电路。与双稳态多谐振荡器不同,单稳态多谐振荡器只要一个安稳状况和一个暂稳态。在没有外部触发的情况下,单稳态多谐振荡器会坚持在它的安稳状况。但是,当单稳态多谐振荡器接收到一个触发信号时,它会从安稳状况转变到暂稳态,并在一段预订的时刻后主动回来到安稳状况。这个预订的时刻一般被称为单稳态多谐振荡器的时刻常数或延时时刻。

单稳态多谐振荡器的暂稳态时刻是由电路中的电阻电容元件决议的。这个特性使得单稳态多谐振荡器很合适用作守时器或延时器,可以在必定的时刻后触发一个事情或操作。

单稳态多谐振荡器的完成方法能有多种,常见的包含运用RC电路、晶体管集成电路等。例如,运用MOSFET和RC电路的单稳态多谐振荡器便是一种常见的完成方法。

总的来说,单稳态多谐振荡器是一种具有单一安稳状况和暂稳态的电子电路,可以在接收到触发信号后发生一段预订的延时时刻,然后主动回来到安稳状况。这种电路在守时器、延时器、脉冲发生器等范畴有广泛的运用。

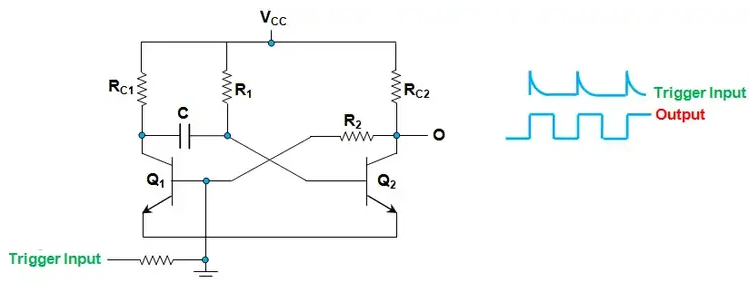

单稳态多谐振荡器可以正常的运用各种组件构建,例如晶体管、运算放大器或 555 守时器IC。在这里,咱们将解说运用两个双极结型晶体管 ( BJT )的单稳态多谐振荡器的作业原理。

该电路由两个BJT Q1和Q2、一个电容器C和四个电阻器RC1、RC2、R1和R2组成。电路的输出取自Q2的集电极。

开端,电路处于安稳状况,其间 Q1 封闭,Q2 敞开。因为 Q2 的集电极接地短路,输出为低电平。电容器 C 的右极板衔接到 Q2 的基极,电压为 0.7 V,而电容器 C 的左极板经过 R1 逐步向 VCC 充电。

当正触发脉冲T施加到Q1的基极时,Q1导通并经过RC1传导电流。这导致 Q1 的集电极和电容器 C 的左极板接地。电容器 C 经过 R1 和 Q1 放电,在其极板上发生负电压。该负电压会封闭 Q2,因为其基极-发射极结是反向偏置的。

电路的这种状况不安稳,因为 Q1 导通而 Q2 截止。因为 Q2 的集电极处于 VCC,因而输出为高电平。电容器C持续放电,直到其电压到达零。

此刻,Q2的基极-发射极结再次变为正向偏置,Q2导通。这导致 Q2 的集电极和电容器 C 的右极板接地。电容器 C 再次开端经过 R2 和 Q2 充电,在其极板上发生正电压。该正电压会封闭 Q1,因为其基极-发射极结是反向偏置的。

电路回来到安稳状况,其间 Q1 封闭,Q2 敞开。因为 Q2 的集电极接地短路,输出为低电平。电容器C持续充电,直到其电压到达0.7V。

接下来小编给大家伙儿一起来共享一些单稳态多谐振荡器电路图,以及简略剖析它们的作业原理。

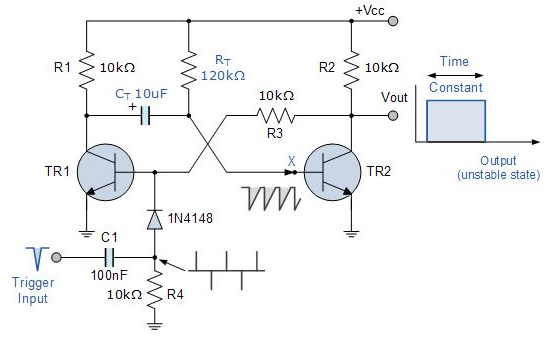

根本的集电极耦合晶体管单稳态多谐振荡器电路及其相关波形如上所示。初次通电时,晶体管TR2的基极经过偏置电阻R T衔接到Vcc,然后将晶体管“彻底导通”并进入饱满状况,一起在此进程中将TR1变为“关断”。然后,这代表具有零输出的“安稳状况”电路。流入的饱满基极点当时TR2因而将等于IB =(VCC - 0.7)/ R Ť。

假如现在在输入端施加一个负触发脉冲,则该脉冲的敏捷下降沿将直接经过电容器C1经过阻隔二极管将其导通到晶体管TR1的基极TR1。TR1的集电极先前为Vcc,敏捷下降至零伏以下,然后有效地使电容器C T跨其极板的负电荷为-0.7v。该动作导致晶体管TR2现在在点X处具有负基极电压,然后使晶体管彻底“截止”。然后,这表明电路的第二状况,即“不安稳状况”,输出电压等于Vcc。

守时电容器C T开端经过守时电阻R T对此-0.7v放电,企图充电至电源电压Vcc。晶体管TR2的基极处的该负电压开端以由R T C T组合的时刻常数确认的速率逐步减小。当TR2的基极电压添加回到Vcc时,晶体管开端导通,因而再次将晶体管TR1变为“ OFF”。这导致单稳态多谐振荡器主动回来其原始安稳状况,等候第二个负触发脉冲再次从头再发动该进程。

当输入被触发时,单稳态多谐振荡器电路发生固定的脉冲宽度。输入馈送到 CR1,CR1 应该是集电极开路源,因为在该电路的输出上呈现活动状况期间,TR1 会将输入短路到地。

该电路的输出从 TR2 的集电极引出。该单稳态多谐振荡器输出脉冲宽度可在 0.5 至 300 毫秒之间改变,经过 1M 微调电位器R5 进行调理。

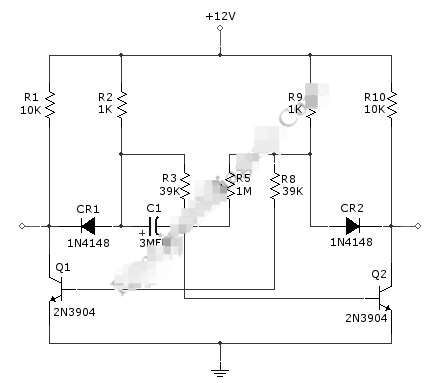

下面的电路是一个单稳态多谐振荡器。单稳态多谐振荡器也称为单稳态多谐振荡器或守时器。该电路的根本功能是发生固定宽度的脉冲。该脉冲的宽度由规划电路时挑选的元件值决议。

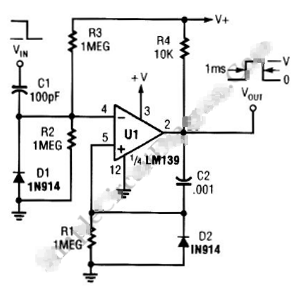

该电路的首要元件是LM139,而且该电路仅运用了四颗LM139的一段。该电路的脉冲宽度由C2和R1的值决议。挑选R1值时,应挑选R4的10倍以上,以防止负载效应。

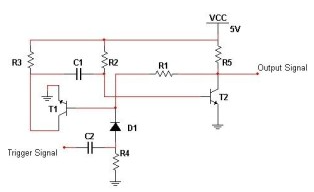

上述电路中,在没有一点外部触发信号的情况下,晶体管T1的基极处于地电平,集电极处于较高电位。因而,晶体管截止。但是,晶体管T2的基极经过电阻从VCC取得正电压供应,晶体管T2被驱动至饱满。而且,因为输出引脚经过T2接地,因而处于逻辑低电平。

当触发信号施加到晶体管 T1 的基极时,跟着基极电流的添加,晶体管 T1 开端导通。当晶体管导通时,其集电极电压下降。一起,电容器C2的电压开端经过T1放电。这导致T2基极电位下降,终究T2截止。因为输出引脚现在经过电阻器直接衔接到正电源:Vout 处于逻辑高电平。

一段时刻后,当电容器彻底放电时,它开端经过电阻器充电。晶体管T2基极点子的电位开端逐步添加,终究驱动T2导通。因而,输出再次处于逻辑低电平或许电路回来到其安稳状况。

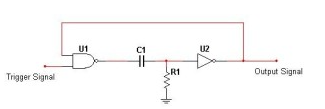

开端,电阻器两头的电位处于地电平。这在某种程度上预示着非门的输入端有一个低逻辑信号。因而,输出处于逻辑高电平。因为与非门的两个输入均为逻辑高电平,因而输出为逻辑低电平,电路输出坚持安稳状况。

现在,假定给与非门的一个输入端一个逻辑低信号,另一个输入端为逻辑高电平,则该门的输出为逻辑1,即正电压。因为R两头存在电位差,VR1处于逻辑高电平,因而非门的输出为逻辑0。当该逻辑低信号反应到与非门的输入端时,其输出坚持为逻辑1,电容器电压开端逐步添加。这又导致电阻器两头的电位降,即VR1开端逐步减小,并在某一点变低,使得逻辑低信号被馈送到非门的输入,而且输出再次处于逻辑高信号。输出坚持安稳状况的时刻由 RC 时刻常数决议。

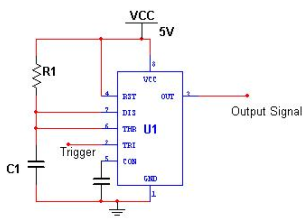

为了在单稳态形式下衔接 555 守时器,需要在放电引脚 7 和地之间衔接一个放电电容器。生成输出的脉冲宽度由放电引脚、Vcc 和电容器 C 之间的电阻器 R 的值决议。

假如你了解555守时器的内部电路,你必定知道555守时器是由一个晶体管、两个比较器和一个SR触发器组成的。

开端,当输出处于逻辑低信号时,晶体管T被驱动至导通而且引脚7接地。假定逻辑低信号施加到触发输入或比较器的输入,因为该电压小于 1/3Vcc,比较器 IC 的输出变高,导致触发器复位,使得输呈现在为处于逻辑低电平。

一起,晶体管封闭,电容器开端经过 Vcc 充电。当电容器电压添加超越 2/3Vcc 时,比较器 2 输出变高,导致 SR 触发器置位。因而,在由 R 和 C 值确认的必守时刻段后,输出再次处于安稳状况。